### 研究課題別評価

- 1 研究課題名:履歴に基づき再構成するマイクロプロセッサの研究

- 2 研究者氏名:佐藤寿倫

## 3 研究の狙い:

現在に至る半導体技術の進歩によって、1 チップ上に 10 億個ものトランジスタを集積可能な時代が目前に迫っている。これはコンピュータにおける演算処理資源の増大を意味しており、1 チップスーパーコンピュータの実現が期待される。しかしながら一方で、集積度の向上はこれまで顧みる必要の無かった様々な新しい問題を提示している。それらは、省電力と信頼性である。

消費電力を削減しようとする動機としては、これまでは主に携帯機器の動作時間を延長したいという要望が主だった。しかし、集積度が向上するにつれて、ハイエンドのマイクロプロセッサにおいても消費電力はもはや無視できないものとなってきた。消費電力を削減する最も有効な方法は電源電圧を下げることである。消費電力は電源電圧の二乗に比例するので、極めて有効な方法と言える。この電源電圧を下げることにも問題がある。その一つは、閾値電圧を下げることによるリーク電流の増大である。電源電圧を下げるとトランジスタの性能が低下する。これを補うためには閾値電圧も下げなければならない。その結果、リーク電流が増えてしまう。リーク電流は回路が動作していないときにも流れてしまう電流で、半導体の性質上取り除くことはできない。つまり、使用時の電力を削減出来る代わりに使用しない時の電力が増えることになる。したがって、アダプティブに閾値電圧を変化させるなどのアーキテクチャを検討する必要があると言える。

微細化の進展はハードウエア故障、特に過渡故障の問題を顕在化させている。過渡故障とは、様々な雑音源が間違った結果を引き起こしてしまうランダムな現象である。例えば、宇宙線などによりダイナミック回路の電荷が変化してしまい、間違った結果を引き起こすことがあり得る。これをソフトエラーと呼ぶ。現状ではこのような故障は稀であるが、半導体技術の進展に伴う微細化によって雑音に対するマージンや信頼度が低下しつつあるのみならず、故障による影響度の増大が予測されている。世代毎に8%の割合で故障率が増大していると言われている。特に携帯機器は劣悪な環境下で使用されるため、これらの応用領域で利用されるマイクロプロセッサの故障に対する耐性、すなわちフォールトトレランス技術の検討が必要と言える。

故障は外因に大き〈影響されます。例えばペンシルベニア州立大学のアーウィンらは、電源電圧を 5V から 3V に下げると故障率が 7 から 8 倍大き〈なると報告している。つまり、省電力と信頼性とはトレードオフの関係にあると言える。両方を同時に改善することはできない。故障率を下げるためには電源電圧を上げるべきですが、そうすると消費電力が増大してしまう。また、使用される環境も影響する。例えば、航空機内での故障率は地表での故障率の 100 倍にもなると言われている。つまり、省電力と信頼性とのトレードオフを考慮した、環境に適応するプロセッサアーキテクチャが求められており、それこそが本研究の目的である。

この目的を達成するために、「動的な実行履歴を利用してハードウエア・ソフトウエアを再構成するマイクロプロセッサアーキテクチャ」に関する研究を行った。マイクロプロセッサは、アプリケーションプログラムの実行時にそのプログラムの環境に適応し、省電力と信頼性とのトレードオフを考慮して動作を特徴付ける履歴を獲得し保存する。この動的な実行履歴を利用して、プロセッサはそのプログラムに最適になるように自身を再構成する。再構成はプログラムの実行と並行して行われる。最適とは、高性能を意味するだけでなく、消費電力の削減やフォールトトレランス性なども含んでいる。例えば、不要な演算器への電源供給を止める再構成は電力削減につながると考えられる。

## 4 研究成果:

### 本研究では、主に

メモリ要素におけるリーク電流削減 故障の検出とそこからの回復機構 演算器配列の有効利用

履歴情報の獲得方法

について検討した。研究を進めるうえでは、まず方式を考案し、続いてそれをソフトウエア・シミュレータとして実現することで評価を行う、という方法を選択した。現在のマイクロプロセッサは非常に大規模なシステムなので、研究段階で実際に作成することは困難である。そこで、このようなコンピュータ上で評価を行うことができる方法を選んだ。続いて、上の3方式についての成果を説明する。

# 4.1 メモリ要素におけるリーク電流削減:

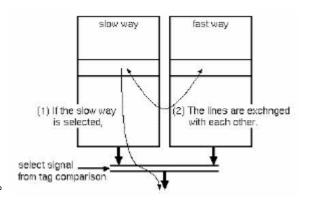

前節で説明したリーク電流増加の問題を解決するために、非均一アクセス時間キャッシュを考案した。図のように非均一アクセス時間キャッシュでは、キャッシュをウエイ単位で、高閾値で低速な CMOS を使用する領域と低閾値で高速な CMOS を使用する領域で構成することにより、リーク電流の削減を実現している。また、低速ウエイのデータが参照された場合には高速ウエイのデータと入れ替えを行う。データの参照には局所性があるので、この入

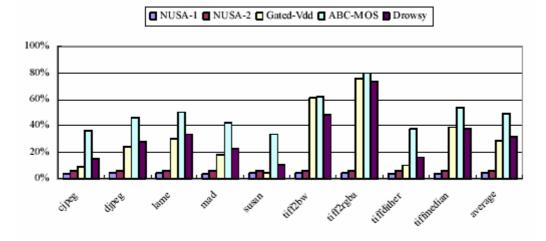

れ替えによってアクセス頻度の高いデータは高速ウエイに配置され、アクセス頻度の低いデータは低速ウエイに配置されると期待される。アクセス頻度の高いデータは重要であると考えられるので、重要度に基づいてデータの再配置を行っていることになる。重要なデータだけを高速ではあるが電力消費の大きいウエイに配置することで、性能低下を抑えつつ省電力を実現した。グラフに表されている結果からわかるように、本方式(NUSA-1およびNUSA-2)は従来の方式(Gated-Vdd, ABC-MOS, Drowsy)のいずれよりも優れており、省電力効果が高いことがわかる。

図:消費エネルギーの自乗と実行時間の積

## 4.2 故障の検出とそこからの回復機構:

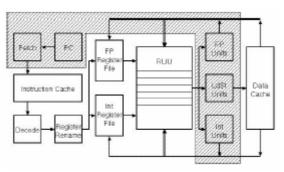

提案する機構は算術演算器や論理演算器で発生した過渡故障を検出できる。つまり故障の検出範囲は右図に斜線で示される部分である。これらの演算器に注力する理由は、現在のマイクロプロセッサの多くではこれらが故障検出の対象となっていないことである。命令キャッシュ、レジスタファイル、そして命令ウインドウ(図中RUU)は他の方法(例えば、パリティや ECC)を

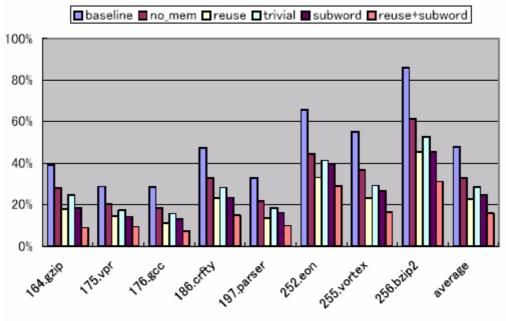

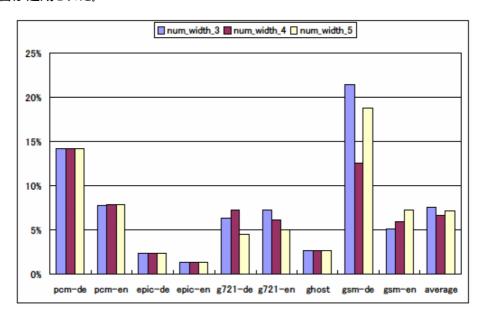

用いて保護されていなければならないが、それは現在のマイクロプロセッサでもすでに一般的に行われている。過渡故障を検出するために命令を複製し二つの結果を比較することを提案した。一度実行を終えた命令を再度実行するために、命令再発行と呼んでいる機構を利用する。これらの命令は命令ウインドウ内部で再発行され、再び演算器で実行される。最初の演算結果は命令ウインドウ中に保持しておく。二度目の演算が完了すると最初の演算結果と比較する。二つの結果が一致しない場合に、過渡故障が検出されたことになる。以上を特別工夫無く実施すると、プロセッサの性能が著しく低下してしまう。実験の結果から、プログラムの実行時間が平均で 50%も長くなることが判明した。この問題を解決するために、計算冗長性の利用やサブワード並列性の利用などを検討した。その結果、グラフに示されるとおり、実行時間の増大を平均で 15%にまで抑えることに成功した。言い換えると、一世代前のコンピュータの性能で満足できるなら、故障からコンピュータを守る安全性を手に入れることができる、というわけである。

図:プログラムの実行時間増加率

# 4.3 演算器配列の有効利用:

一般に省電力化を進めるとマイクロプロセッサの性能は低下してしまう。したがってマイクロプロセッサの性能を向上させる方式の検討が必要であるが、従来のような単純に演算器を追加させる方式では性能向上に限界がある。それは、近年問題視されている配線遅延の影響を大きく被るからである。演算結果を長いバスを用いて転送すると配線遅延の問題を大きく被ってしまい、マイクロプロセッサの動作速度が低下してしまう。つまり性能が低下してしまう。この問題を解決するために、バスやレジスタファイルを介さず、演算結果を演算器間で直接通信する方式を考案した。つまり多数の演算器が配列状に配置されることになる。この方式で性能向上させるためには、多数

の演算器を有効利用できる必要がある。そこで中間結果を求める命令の連鎖に着目し、結果が一度だけしか利用されない命令に着目して、配列状の演算器に割り付けることを検討した。実行時に以上のような命令を検出する必要があるので、なんらかのハードウエア支援が必要である。このための機構として、連想検索を必要としない単純な方式を考案した。単純であるので高速動作が期待できる。さらに演算に用いられるオペランドのビット幅に着目し、ビット幅の小さなオペランドを用いる演算であれば 1 サイクル内に複数演算実行できる機構を提案した。以上により約10%の性能改善が達成された。

図∶性能向上率

# 4.4 履歴情報の獲得方法:

マイクロプロセッサをプログラムに適応させるためには、プログラムの性質を知る必要がある。そのためには、一般に履歴情報を収集する。これは非常に手間のかかる作業であった。情報収集するためのプログラムを一度実行し、その情報をもとにプログラムを書き換えるという作業になるからである。情報収集するためのプログラムは、本来のプログラムよりも3倍以上遅いということが実験でわかった。この問題を解決するために、プログラム自体には手を入れないで、そのプログラムと同時に情報収集するための別のプログラムを実行する方式を考案した。この方式を導入すると、実行時間の増大を40%まで削減できることができる。

# 5 自己評価:

これまで検討してきた方式は十分な成果が得られていると思われるが、最初に述べた研究目標が達成できているとは言えない。なぜなら、個々の方式が独立に検討されているだけだからである。したがって最終目標を達成するためには、これまで検討してきた方式を組み合わせることが必要である。組み合わせると、これまでは発見できなかった問題が顕在する課も知れない。つまり今後は、これまでの成果を踏まえて、最終目標を達成できるような統合システムを構築し評価することが必要である。以上を経て、最終的な目標が達成されるという展望となる。

# 6 研究総括の見解:

1 チップ上に 10 億個ものトランジスタが集積可能な時代の新しい問題、省電力と信頼性とのトレードオフを考慮した、環境に適応するプロセッサアーキテクチャの研究である。佐藤研究者の動的な実行履歴を利用してハードウエア・ソフトウエアを再構成するという着目点は新鮮で、ユニー

クである。メモリ要素におけるリーク電流削減問題では非均一アクセス時間キャッシュ方式、信頼性向上問題では故障の検出とその回復機構、性能向上問題では演算器配列の直接通信方式、履歴情報獲得の高速化手法においてそれぞれ成果を挙げた。今後、個々に検討されてきた方式を組み合わせた統合システムを構築し評価されることを期待している。

### 7 主な論文等:

受賞 情報処理学会 山下記念研究賞(H15年度)

### 論文

- Toshinori Sato, "Exploiting Trivial Computation in Dependable Processors," 20th International Conference on Computers and Their Applications (CATA), March 2005 (in press).

- (2) 森下大輔, <u>佐藤寿倫</u>, "演算器アレイ型プロセッサへのアプリケーション実装における課題," 情報処理学会第67回全国大会, March 2005.

- (3) Takamasa Tokunaga, <u>Toshinori Sato</u>, "Profiling with Helper Threads," International Conference on Parallel and Distributed Computing and Networks (PDCN), February 2005.

- (4) <u>佐藤寿倫</u>, "性能低下ゼロを目指した耐過渡故障マイクロプロセッサ," 信学技報 CPSY2004-60, pp.73-76, December 2004.

- (5) <u>Toshinori Sato</u>, "Exploiting Sub-word Parallelism for Dependable Processors," WSEAS Transactions on Information Science and Applications, issue 6, vol.1, pp.1051-1056, December 2004.

- (6) <u>Toshinori Sato</u>, "Exploiting Sub-word Parallelism for Dependable Processors," 5<sup>th</sup> International Conference on Automation & Information (ICAI), CD-ROM, November 2004.

- (7) Seiichiro Fujii, <u>Toshinori Sato</u>, "Non-Uniform Set Associative Caches for Power-Aware Embedded Processors," International Conference on Embedded and Ubiquitous Computing (EUC), pp.217-226, August 2004.

- (8) Akihito Sakanaka, Seiichirou Fujii, <u>Toshinori Sato</u>, "A Leakage-Energy-Reduction Technique for Highly-Associative Caches in Embedded Systems," ACM SIGARCH Computer Architecture News, vol.32, issue 3, pp.50-54, June 2004.

- (9) 藤井誠一郎,千代延昭宏,<u>佐藤寿倫</u>,"データの重要度を利用した省電力キャッシュ,"先 進的計算基盤システムシンポジウム(SACSIS), pp.123-124, May 2004.

- (10) Masaharu Goto, <u>Toshinori Sato</u>, "Leakage Energy Reduction in Register Renaming," 1<sup>st</sup> International Workshop on Embedded Computing Systems (EC) held in conjunction with 24th International Conference on Distributed Computing Systems (ICDCS), pp.890-895, March 2004.

- (11) Hidenori Sato, <u>Toshinori Sato</u>, "A Static and Dynamic Energy Reduction Technique for I-Cache and BTB in Embedded Processors," Asia and South Pacific Design Automation Conference (ASP-DAC), pp.831-834, January 2004.

- (12) <u>Toshinori Sato</u>, Daisuke Morishita, "A Field-Customizable and Runtime-Adaptable Microarchitecture," 2nd International Conference on Field-Programmable Technology (FPT), pp.328-331, December 2003.

- (13) 森下大輔, <u>佐藤寿倫</u>, "履歴を利用して多数の演算器を有効利用するプロセッサの研究," 第7回システムLSI ワークショップ, pp.315-318, November 2003.

- (14) Akihito Sakanaka, <u>Toshinori Sato</u>, "A Leakage-Energy-Reduction Technique for High-Associativity Caches in Embedded Systems," Workshop on Memory Access Decoupled Architectures and Related Issues (MEDEA) held in conjunction with 12<sup>th</sup>

- International Conference on Parallel Architectures and Compilation Techniques (PACT), pp.51-56, September 2003.

- (15) 藤井誠一郎, 坂中昭仁, <u>佐藤寿倫</u>, "参照の局所性を利用したキャッシュメモリのリーク電流削減手法," 第11 回電子情報通信学会九州支部学生会講演会, pp.104, September 2003.

- (16) 佐藤秀則, 藤井誠一郎, <u>佐藤寿倫</u>, "ループキャッシュによる命令キャッシュ及び分岐予測器の電力削減,"第11回電子情報通信学会九州支部学生会講演会, pp.105, September 2003.

- (17) <u>佐藤寿倫</u>, 森下大輔, 濱田哲也, 藤井誠一郎, "履歴に基き適応可能なマイクロアーキテクチャの実現へ向けて," 第1回リコンフィギャラブルシステム研究会, pp.7-13, September 2003

- (18) Akihito Sakanaka, <u>Toshinori Sato</u>, "Reducing Static Energy of Cache Memories via Prediction-Table-less Way Prediction," 13th International Workshop on Power And Timing Modeling, Optimization and Simulation (PATMOS), pp.530-539, September 2003.

- (19) Takenori Koushiro, <u>Toshinori Sato</u>, "An Energy-Efficient Speculative Chip-Multiprocessor Utilizing Trace-level Value Prediction," 1st Value-Prediction Workshop (VPW1) held in conjunction with 30th International Symposium on Computer Architecture (ISCA), pp.79-85, June 2003.

### 口頭発表

(20) Toshinori Sato, "Do Embedded Processors Benefit from Adaptability?," 6th International Workshop on Innovative Architecture for Future Generation High-Performance Processors and Systems (IWIA), January 2003.

# 特許

発 明 者:佐藤寿倫

発明の名称∶キャッシュメモリ

出 願 人:科学技術振興事業団

出 願 日:平成14年10月8日

発 明 者:佐藤寿倫

発明の名称:キャッシュメモリ

出 願 人:科学技術振興事業団

出 願 日:平成14年12月27日

発 明 者:佐藤寿倫

発明の名称:キャッシュメモリ、及びキャッシュメモリの電力削減方法

出願人:九州工業大学長 出願日:平成15年4月23日

発 明 者:佐藤寿倫

発明の名称:電力制御装置 出願人:九州工業大学長 出願日:平成15年4月30日